# Actively Tunable Lossless Floating Inductance Simulator Using Voltage Differencing Buffered Amplifiers

Orapin Channumsin and Worapong Tangsrirat, Member, IAENG

Abstract— This work describes the topology for simulating the floating inductance simulator circuit based on employing voltage differencing buffered amplifiers (VDBAs) as new active components. The realized floating inductance simulator circuit uses two VDBAs and only one grounded capacitor. The synthetic circuit is resistorless and canonical structure as well as attractive for integration. The resulting equivalent inductance value of the proposed simulator can be adjusted electronically through the transconductance parameter of the VDBA. As illustrative application example, the proposed tunable floating inductance simulator is employed to realize the second-order RLC bandpass filter. Simulation results using standard 0.35-\(mu\) m BiCMOS process model are included to verify the theoretical analysis.

Index Terms— Voltage Differencing Buffered Amplifier (VDBA), voltage-mode circuit, floating inductance simulator

## I. INTRODUCTION

Floating inductance simulation circuit is one of the most important circuit elements widely used in many applications such as oscillator design, filter design and cancellation of parasitic elements. However, unfortunately, a large-valued physical inductor is not allowed to fabricate in the integrated circuit technology because of a large chip area and high-cost requirements. Although on chip spiral inductors with low quality factor (Q) can be performed to alleviate this restriction, their values are very small, usually in order of 1 nH. Accordingly, to overcome this problem, many actively simulated floating inductor circuits using various high-performance active devices have been reported in literature [1]-[10]. However, all of them need a large number of active and passive elements for their realizations.

Lately, the new active building block called voltage differencing buffered amplifier (VDBA) is introduced in [11], to provide the alternative possibility of electronically controllable voltage-mode analog signal processing circuits

Manuscript received May 10, 2016; revised June 13, 2016.

This work was supported by Faculty of Engineering, Department of Electronic and Telecommunication Engineering, Rajamangala University of Technology Isan (RMUTI), Khon-kaen Campus.

O. Channumsin is with the Faculty of Engineering, Rajamangala University of Technology Isan (RMUTI), Khon-kaen Campus, Srichan road, Muang, Khon kaen 40000, Thailand (e-mail: orapin.ch@rmuti.ac.th).

Worapong Tangsrirat is with the Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang (KMITL), Chalongkrung road, Ladkrabang, Bangkok 10520, Thailand (phone: +662-326-4205; fax: +662-326-4205; e-mail: worapong.ta@kmitl.ac.th).

and solutions. Several applications based on using VDBAs as active elements in mainly analog signal processing have been developed [12]-[20]. This work presents an actively floating lossless inductance simulator topology using only two VDBAs and one grounded capacitor. The proposed synthetic floating inductor is electronically tunable through the transconductance gains of the VDBAs. The performance of the proposed floating simulator circuit is provided for illustrative example of the active RLC bandpass filter design. PSPICE simulation results with standard 0.35- $\mu$ m BiCMOS process parameters are obtained to confirm the theory.

#### II. DESCRIPTION OF THE VDBA

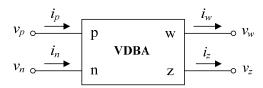

As symbolically shown in Fig.1, the VDBA is a four-terminal versatile active building block, which consists of high-impedance voltage differencing input terminals p and n, high-impedance current output terminal z, and low-impedance output of voltage buffer noted as w. The terminal relations of the VDBA can be expressed by the following matrix equation:

$$\begin{bmatrix} i_p \\ i_n \\ i_z \\ v_w \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ g_m & -g_m & 0 & 0 \\ 0 & 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} v_p \\ v_n \\ v_z \\ i_w \end{bmatrix}$$

(1)

In (1), the parameter  $g_m$  refers to the transconductance gain of the VDBA, which normally is controlled by electronic means through the external supplied current or voltage.

Fig. 1. Circuit representation of the VDBA.

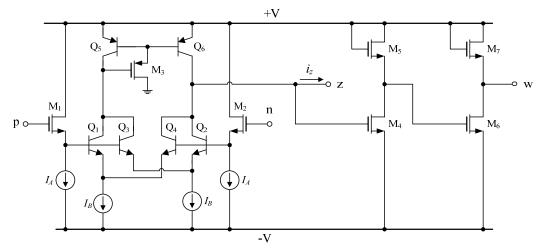

Fig.2 BiCMOS implementation of the VDBA.

Fig.2 shows the schematic BiCMOS realization of the VDBA [21], which mainly consists of the input stage consists of input transistors  $M_1$ - $M_2$ ,  $Q_1$ - $Q_4$ , and current mirror transistors  $Q_5$ - $Q_6$ ,  $M_3$ . Transistors  $M_4$ - $M_5$  and  $M_6$ - $M_7$  represents the output stage, which constitute the terminal w. In this structure, the effective small-signal transconductance  $(g_m)$  can be derived as:

$$g_m = \frac{I_B}{2V_T} \tag{2}$$

where  $V_T \approx 26 \text{ mV}$  at  $27^{\circ}\text{C}$  is the thermal voltage. It may be easily visualized that the  $g_m$ -value is tunable linearly and electronically by an external DC bias current  $I_B$ .

Moreover, if we assume that the transistors  $M_4$ - $M_7$  are biased to operate in the active region. As a result, the small-signal voltage gain between  $v_w$  and  $v_z$  is approximated to:

$$\frac{v_w}{v_z} \cong \frac{g_4 g_6}{g_5 g_7} \tag{3}$$

where  $g_i$  denotes the conductance of transistor  $M_i$  (i = 4, 5, 6, 7). Also assume that  $g_4 \cong g_5$  and  $g_6 \cong g_7$ , thus  $v_w \cong v_z$  as expected.

### III. PROPOSED FLOATING INDUCTANCE SIMULATOR

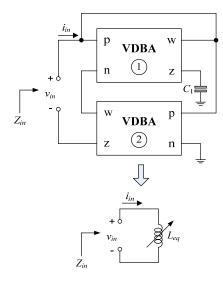

Fig.3 shows the proposed floating inductance simulator circuit constructing only two VDBAs and one grounded capacitor without needing any external passive resistors. The synthetic inductor is, therefore, canonical number of active and passive components and also preferable for further integration point of view. Circuit analysis yields the input impedance for the proposed floating inductor in Fig.3 as:

$$Z_{in} = \frac{v_{in}}{i_{in}} = \frac{sC_1}{g_{m1}g_{m2}} \tag{4}$$

where  $g_{mi}$  is the transconductance value of *i*-th VDBA (i = 1, 2). Thus, it can be realized that the circuit of Fig.3 simulates a floating inductor with an equivalent inductance ( $L_{ea}$ ):

$$L_{eq} = \frac{C_1}{g_{m1}g_{m2}} \tag{5}$$

It is clearly seen from (5) that the  $L_{eq}$ -value can be adjusted electronically by controlling the values of  $g_{m1}$  and/or  $g_{m2}$ .

Fig. 3. Proposed lossless floating inductance simulator using VDBAs.

#### IV. NON-IDEAL EFFECTS OF THE VDBA

## A. Non-Ideal Transfer Gain Effects

Considering the non-ideal transfer gains of the VDBA, the port relationship from (1) can be re-expressed by the following matrix equation:

$$\begin{bmatrix} i_{p} \\ i_{n} \\ i_{z} \\ v_{w} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ \alpha g_{m} & -\alpha g_{m} & 0 & 0 \\ 0 & 0 & \beta & 0 \end{bmatrix} \begin{bmatrix} v_{p} \\ v_{n} \\ v_{z} \\ i_{w} \end{bmatrix}$$

(6)

where  $\alpha$  and  $\beta$  are the transconductance inaccuracy and the non-ideal voltage gain of the VDBA, respectively. The simulator of Fig.3 is re-analyzed using (6), and the non-idel input impedance function is modified to be:

$$Z_{in} = \frac{sC_1}{\alpha_1 \alpha_2 \beta_1 \beta_2 g_{m1} g_{m2}} \tag{7}$$

Normalized various sensitivities of  $Z_{in}$  with respect to active and passive components calculated from (7) are given by:

$$S_{\sigma}^{Z_{in}} = S_{\sigma}^{Z_{in}} = -1 \tag{8}$$

$$S_{\alpha_1}^{Z_{in}} = S_{\alpha_2}^{Z_{in}} = S_{\beta_1}^{Z_{in}} = S_{\beta_2}^{Z_{in}} = -1$$

(9)

and

$$S_{C_i}^{Z_{in}} = 1$$

(10)

which are all no more than unity in absolute value. Therefore, it can be realized that the proposed inductor in Fig.3 exhibits low sensitivity performance.

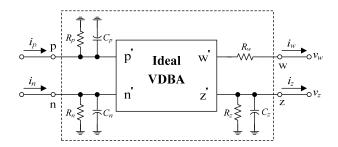

$Fig.\ 4.\ \ Non-ideal\ model\ of\ the\ VDBA\ including\ its\ parasitic\ elements.$

## B. Parasitic Impedance Effects

The effects of various parasitic impedances of the VDBA used in the proposed inductor is taken into consideration. In practice, the behavior model of the VDBA consisting various non-ideal parasitic elements can be shown in Fig.4. Let  $R_p$ ,  $R_n$ ,  $R_z$  and  $R_w$  represent the parasitic resistances and  $C_p$ ,  $C_n$  and  $C_z$  denote the parasitic capacitances of the corresponding terminals of the VDBA. The proposed inductor of Fig.3 is re-analyzed taking into consider the above parasitic effects. In this case, it can be seen that, at the terminal z of the VDBA1, the parasitic impedances  $R_z/\!/C_z$  appearing in parallel with the external grounded capacitor  $C_1$  bring an extra parasitic pole  $(\omega_p)$  to the synthetic inductor circuit. Assuming  $C_1 >> C_z$ , the extra pole  $\omega_p$  can be defined as:

$$\omega_p \cong \frac{1}{R_z C_1} \tag{11}$$

It should be noted from (11) that the high-frequency performance of the proposed floating inductor would be affected because of this parasitic pole. However, to prevent this effect, the following condition should satisfy such that:

$$\frac{1}{sC_1} \ll R_z \tag{12}$$

#### V. PERFORMANCE SIMULATIONS AND DISCUSSIONS

To verify the theoretical prediction, the proposed circuit in Fig.3 was simulated with PSPICE program. To implement the VDBA device in the following simulation purpose, the BiCMOS technology structure depicted in Fig.2 has been employed using 0.35- $\mu$ m BiCMOS technology [21]. Transistor aspect ratios (W/L in  $\mu$ m/ $\mu$ m) were set as : 14/0.7 and 28/0.7 for all NMOS and PMOS transistors respectively. The DC supply voltages and bias currents were respectively chosen as : +V = -V = 1 V and  $I_A$  = 25  $\mu$ A.

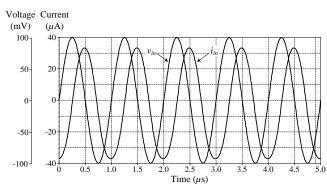

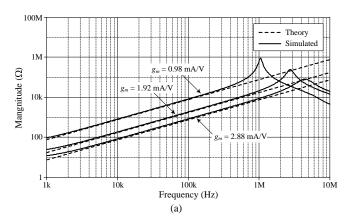

The proposed floating inductor in Fig.3 was simulated with the following active and passive component values :  $C_1$  = 10 nF and  $g_m = g_{m1} = g_{m2} \cong 0.98$  mA/V, 1.92 mA/V, 2.88 mA/V, ( $I_B = I_{B1} = I_{B2} \cong 25 \mu$ A, 50  $\mu$ A and 75  $\mu$ A), which results in :  $L_{eq} = 12.3$  mH, 2.7 mH and 1.2 mH, respectively. Fig.5 shows simulated time-domain responses for  $v_{in}$  and  $i_{in}$  of the input impedance of the proposed inductor. The results obtained from the simulation show that the current  $i_{in}$  lags the voltage  $v_{in}$  by 89°. Fig.6 shows the simulated frequency characteristics for the input impedance of the proposed inductor, which demonstrate that the useful frequency range is approximately from 10 kHz to 800 kHz.

Fig. 5. Simulated time-domain responses for  $v_{in}$  and  $i_{in}$  of the proposed floating inductor of Fig.3.

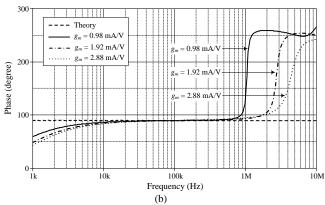

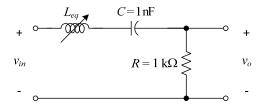

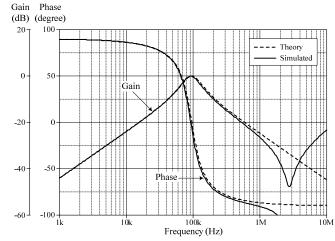

#### VI. APPLICATION TO FILTER REALIZATION

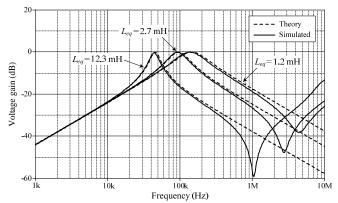

As an application example of the synthetic floating inductance simulator of Fig.3, it is applied in the RLC bandpass filter as shown in Fig.7. The  $L_{eq}$  is simulated with:  $C_1 = 10$  nF and  $g_m = g_{m1} = g_{m2} \cong 1.92$  mA/V ( $I_B = I_{B1} = I_{B2} \cong 50$   $\mu$ A), yielding  $L_{eq} \cong 2.7$  mH. Fig.8 shows the idea and simulated frequency responses of the bandpass filter in Fig.7, which appear that the simulated values are in good agreement with the ideal values. Furthermore, in order to demonstrate the electronic controllability of the proposed

floating inductor, the simulated gain responses of the bandpass filter in Fig.7 with tuning  $L_{eq}$ -value are shown in Fig.9. The value of  $L_{eq}$  in Fig.7 was respectively adjusted to 12.3 mH, 2.7 mH and 1.2 mH, by changing  $g_m = 0.98$  mA/V, 1.92 mA/V, 2.88 mA/V ( $I_B = 25 \mu$ A, 50  $\mu$ A and 75  $\mu$ A). This adjusting leads to obtain the center frequency  $f_c \cong 45.3$  kHz, 96.7 kHz and 145.1 kHz, respectively.

Fig. 6. Simulated frequency responses for  $Z_{in}$  of Fig.3 with various VDBA biasing currents.

(a) magnitude responses (b) phase responses.

Fig. 7. RLC bandpass filter realized with the synthetic floating inductor of Fig.3.

## VII. CONCLUSION

The synthetic lossless floating inductance simulator has been presented in this paper. The simulator contains only two VDBAs and one grounded capacitor, which is desired for further integrated circuit implementation. The equivalent inductance values can be adjusted electronically through the  $g_m$ -values of the VDBAs. The usefulness of the proposed circuit is demonstrated on the RLC bandpass filter design example. The workability of the proposed structure has been supported by PSPICE simulations using standard 0.35- $\mu$ m BiCMOS technology.

Fig. 8. Simulated frequency responses of the bandpass filter in Fig.7 at  $f_c \cong$  96.7 kHz.

Fig. 9. Gain responses of Fig.7 with electronically variable  $L_{eq}$ .

## REFERENCES

- C. Psychalinos and A. Spanidou, "Current amplifier-based grounded and floating inductance simulators". *Int. J. Electron. Commun. (AEU)*, vol. 60, 2006, pp. 168-171.

- [2] E. Yuce, "Inductor implementation using a canonical number of active and passive elements", *Int. J. Electron.*, vol.94, no.4, 2007, pp.317-326.

- [3] E. Yuce, "On the implementation of the floating simulators employing a single active element", *Int. J. Electron. Commun. (AEU)*, vol.61, no.7, 2007, pp.453-458.

- [4] M. Sagbas, U. E. Ayten, H. Sedef and M. Koksal, "Electronically tunable floating inductance simulator", *Int. J. Electron. Commun.* (AEU), vol.63, 2009, pp.423-4278.

- [5] E. Yuce, S. Minaei, "Novel floating simulated inductors with wider operating-frequency ranges", *Microelectron. J.*, vol.40, 2009, pp.928-938.

- [6] D. Prasad, D. R. Bhaskar, and A. K. Singh, "New grounded and floating simulated inductance circuits using current differencing transconductance amplifiers", *Radioengineering*, vol.19, no.1, 2010, pp.194-198.

- [7] E. Yuce, "A novel floating simulation topology composed of only grounded passive elements", *Int. J. Electron.*, vol.97, no.3, 2010, pp.249-262.

- [8] J. W. Horng, "Lossless inductance simulation and voltage-mode universal biquadratic filter with one input and five outputs using DVCCs", Analog Integr. Circuits Signal Process., no.62, 2010, pp.407–413.

- [9] M. A. Ibrahim, S. Minaei, E. Yuce, N. Herencsar and J. Koton, "Lossy/lossless floating/grounded inductance simulation using one DDCC", *Radioengineering*, vol.21, no.1, 2012, pp.3-10.

- [10] U. E. Ayten, M. Sagbas, N. Herencsar and J. Koton, "Novel general element simulators using CBTA", *Radioengineering*, vol.21, no.1, 2012, pp.11-19.

- [11] D. Biolek, R. Senani, V. Biolkova, Z. Kolka, "Active elements for analog signal processing: classification, review, and new proposals", *Radioengineering*, vol. 17 no. 4, 2008, pp.15-32.

- [12] A. Yesil, F. Kacar and K. Gurkan, "Lossless grounded inductance simulator employing single VDBA and its experimental band-pass filter application", *Int. J. Electron. Commun. (AEU)*, vol.68, 2014, pp.143-150.

- [13] F. Kacar, A. Yesil, A. Noori, "New CMOS realization of voltage differencing buffered amplifier and its biquad filter application", *Radioengineering*, vol. 21, no.1, 2012, pp. 333-339.

- [14] N. Khatib and D. Biolek, "New voltage mode universal filter based on promising structure of voltage differencing buffered amplifier", *Proc.* of The 23<sup>th</sup> Radioelektronika, April 16-17, Pardubice, Czech Republic, 2013, pp. 171-181.

- [15] R. Sotner, J. Jerabek, N. Herencsar, "Voltage differencing buffered/inverted amplifiers and their applications for signal generation", *Radioengineering*, vol.22, no.2, 2013, pp.490-504.

- [16] A. Gilney, E. Alaybeyoglu and H. Kuntman, "New CMOS realization of z copy voltage differencing buffered amplifier and its current-mode filter appliction", *Proc. of The 8<sup>th</sup> DTIS*, March 26-28, Abu Dhabi, United Arab Emirates, 2013, pp. 68–71.

- [17] S. Unhavanich, O. Onjan and W. Tangsrirat, "Tunable capacitance multiplier with a single voltage differencing buffered amplifier", Lecture Notes in Engineering and Computer Science: Proceedings of The International MultiConference of Engineers and Computer Scientists 2016, IMECS 2016, 16-18 March, 2016, Hong Kong, pp. 568-571.

- [18] P. Whig and S. N. Ahmad, "CMOS integrated VDBA-ISFET device for water quality monitoring", *International Journal of Intelligent Engineering and Systems*, vol. 7, no.1, 2014.

- [19] O. Channumsin and W. Tangsrirat, "Actively synthetic floating inductor using voltage differencing buffered amplifiers", Lecture Notes in Engineering and Computer Science: Proceedings of The International MultiConference of Engineers and Computer Scientists 2016, IMECS 2016, 16-18 March, 2016, Hong Kong, pp. 620-623.

- [20] W. Tangsrirat, "Simple BiCMOS realization of full balanced voltage differencing buffered amplifier", Revue Roumaine Des Sciences Techniques (Rev. Roum. Sci. Techn. – Électrotechn. et Énerg), vol.60, no.4, 2015, pp.409-415.

- [21] W. Tangsrirat, O. Onjan, T. Pukkalanun, "BiCMOS realization of voltage differencing buffered amplifier (VDBA) and its application", Proc. of The 29th ITC-CSCC, July 1-4, Phuket, Thailand, 2014.