# Design Methodology for a Maximum Sequence Length MASH Digital Delta-Sigma Modulator

Tao Xu and Marissa Condon \*

Abstract—The paper proposes a novel structure for a MASH digital delta-sigma modulator (DDSM) in order to achieve a long sequence length. The expression for the sequence length is derived. The condition to produce the maximum sequence length is also stated. It is proved that the modulator output only depends on the structure of the first-order error feedback modulator (EFM1) which is the first stage of a Multi-stAge noise SHaping (MASH) modulator.

Keywords: MASH, Delta-Sigma Modulation, Sequence Length, Multi-Modulii, Co-Prime Numbers.

## 1 Introduction

Fractional-N Frequency Synthesizers [1] are widely used in modern communication systems. In general, they work as Local Oscillators (LO) to generate the exact required frequencies. The digital delta-sigma modulator (DDSM) acts as the controller of the multi-modulus frequency divider in the feedback loop of the frequency synthesizer. The most attractive property of DSMs is that they push most of the quantisation noise to higher frequencies and hence out of the useful frequency band. Thus the noise can simply be filtered without affecting the input signal.

Since the DDSM is a finite state machine, when the input is a DC rational constant, the output is always a repeating pattern (limit cycle) [9] [10]. The period of the cycle is termed the sequence length. For this type of input, the quantization noise is periodic. When a sequence length is short, the power is distributed among spurious spurs that appear in the DDSM output spectrum. Hence, there is a desire to break short sequences. Dithering [14] [15] is one of the most commonly employed methods to break the short sequence length. However, it requires extra hardware and inherently introduces additional inband noise. Recently, some design methodologies have been proposed to maximise the sequence length. Borkowski [9] summarises the guaranteed and maximum period obtained by setting the initial condition of the reg-

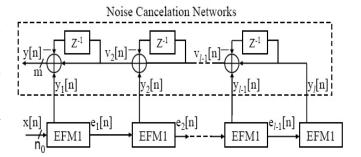

Figure 1: MASH DDSM architecture.

isters in a EFM. Hosseini [16] introduced a digital deltasigma modulator structure termed the HK-MASH with a very long sequence. The period of the HK-MASH is proven by mathematical analysis [16] [17]. This paper proposes a novel design methodology to further increase the modulator sequence length.

In Section 2, the architectures of the classic MASH DDSM and the HK-MASH are reviewed. In Section 3, a novel structure is proposed that results in the maximum sequence length. The expression for the sequence length is derived as well. The simulation results are shown in Section 4.

#### 2 Previous Work

The architecture of an lth order MASH digital deltasigma modulator (DDSM) is illustrated in Fig. 1. It contains l first-order error-feedback modulators (EFM1). x[n] and y[n] are an  $n_0$  bit input digital word and an mbit output, respectively. The relationship between them is

$$mean(y) = \frac{X}{M} \tag{1}$$

where X is the decimal number corresponding to the digital sequence x[n] [16], i.e.,  $x[n] = X \in \{1, 2, ..., M - 1\}$ , and M is the quantizer modulus which is set as  $2^{n_0}$  in the DDSM.

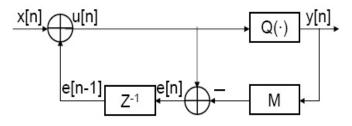

The model of the EFM1 is shown in Fig. 2, which is the central component in the make-up of the MASH digital delta-sigma modulator (DDSM). The rectangle  $Z^{-1}$  represents the register to store the error e[n] and delay it for one sample time.  $Q(\cdot)$  is the quantization function:

<sup>\*</sup>Manuscript submitted ??. This material is based upon works supported by Science Foundation Ireland under Principal Investigator Grant No. 05/IN.1/I18. The authors are with Research Institute for Networks and Communications Engineering (RINCE), School of Electronic Engineering, Dublin City University, Dublin, Ireland Tel/Fax: +353-1-700-5856/5508 Email: taoxu@eeng.dcu.ie; condonm@eeng.dcu.ie

Figure 2: EFM1: First-order error-feedback modulator.

$$y[n] = Q(u[n]) = \begin{cases} 1, & u[n] \ge M \\ 0, & u[n] < M \end{cases}$$

(2)

where

$$u[n] = x[n] + e[n-1].$$

(3)

The maximum sequence lengths for this structure has been found from simulations [9], and are as illustrated in Table 1. To achieve the maximum period, the first stage EFM1 must have an odd initial condition. This is implemented by setting the register.

Table 1: The sequence length summarised in [9].

| Modulator Order | Maximum Period |

|-----------------|----------------|

| 2               | $2^{n_0+1}$    |

| 3               | $2^{n_0+1}$    |

| 4               | $2^{n_0+2}$    |

| 5               | $2^{n_0+2}$    |

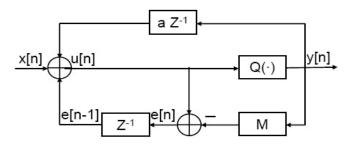

The architecture of the modified EFM1 used in the HK-MASH is illustrated in Fig. 3. The only difference between it and the classic EFM1 in Fig. 2 is the presence of the feedback block  $aZ^{-1}$ . a is a specially-chosen small integer to make (M-a) the maximum prime number below  $2^{n_0}$  [16]. The sequence length of it is  $(2^{n_0} - a)^l \approx (2^{n_0})^l$ . This value will be compared with that of the proposed MASH in Section 4.

Figure 3: HK-EFM1: The modified EFM1 used in HK-MASH.

# 3 The Proposed Structure

In this section, a novel structure for the MASH DDSM is introduced, which produces a long sequence length. The

HK-EFM1, shown in Fig. 3, is utilised to form the new structure. The small positive integer a in ith stage of HK-EFM1 is denoted as  $a_i$ . This value will be assumed to be different for each stage.

The values of  $a_i$  are chosen to make  $\{M - a_1, M - a_2, ..., M - a_l\}$  co-prime numbers to maximise the sequence length, which will be demonstrated in *Theorem 1*. Thus, in an lth order proposed MASH, there are l co-prime numbers around  $2^{n_0}$  that need to be found. The higher the modulator order, the more co-prime numbers that need to be confirmed. This results in greater difficulty in finding suitable values for  $a_i$ . Fortunately, the most popular MASH DDSM in modern communication systems is the 3rd order one [9]. A few values of  $a_i$  chosen by the authors are given in Table 2. Note that in order to make the sequence length independent of the input,  $M - a_1$  is set as a prime number [16] [17]. The difference between a co-prime number and a prime number [20] is stated as below:

- 1. A prime number is a natural number which has exactly two divisors: 1 and itself.

- 2. If the greatest common divisor of any two numbers is 1, they are co-prime numbers. They do NOT have to be prime numbers, such as 8 and 9.

In Theorem 2, it is proven that the required output, mean(y), depends only on the first stage EFM1. Hence,  $M - a_1$  is set as a prime number around  $2^{n_0}$ . This is to make X and  $M_1$  always co-prime numbers and therefore to make the sequence length independent of the value of input. In order to maintain the modulator output accuracy, the value of the input DC X is adjusted to

$$X = (M - a_1) \cdot mean(y) \tag{4}$$

where mean(y) is the required output to control the static frequency divider in a fractional-N frequency synthesizer.

Table 2: Some values of  $a_i$  in proposed MASH 1-1-1.

| ٣. |             |       |       |       |  |  |

|----|-------------|-------|-------|-------|--|--|

|    | Word length | $a_1$ | $a_2$ | $a_3$ |  |  |

|    | 5 bit       | 1     | 0     | 3     |  |  |

|    | 8 bit       | 5     | 0     | 1     |  |  |

|    | 9 bit       | 3     | 0     | 1     |  |  |

|    | 10 bit      | 3     | 0     | 1     |  |  |

|    | 11 bit      | 9     | 0     | 1     |  |  |

**Theorem 1.** If  $\{M-a_1, M-a_2, ..., M-a_l\}$  are co-prime numbers, the sequence length attains its maximum value.

*Proof.* In the first-stage EFM1 illustrated in Fig. 3,

$$e_1[1] = u[1] - y_1[1]M$$

=  $X + e_1[0] + y_1[0]a_1 - y_1[1]M$  (5)

$$e_1[2] = X + e_1[1] + y_1[1]a_1 - y_1[2]M$$

(6)

:

$$e_1[N_1] = X + e_1[N_1 - 1] + y_1[N_1 - 1]a_1 - y_1[N_1]M$$

(7)

The sum of all of the above equations is:

$$\sum_{k=1}^{N_1} e_1[k] = N_1 X + \sum_{k=0}^{N_1 - 1} e_1[k] + \sum_{k=0}^{N_1 - 1} y_1[k] a_1 - \sum_{k=1}^{N_1} y_1[k] M.$$

(8)

Since in the steady state, the first EFM1 is periodic with a period  $N_1$  [17],

$$\sum_{k=1}^{N_1} e_1[k] = \sum_{k=0}^{N_1 - 1} e_1[k]. \tag{9}$$

Hence, (8) may be modified to

$$\sum_{k=1}^{N_1} e_1[k] = N_1 X + \sum_{k=1}^{N_1} e_1[k] + \sum_{k=1}^{N_1} y_1[k] a_1 - \sum_{k=1}^{N_1} y_1[k] M.$$

(10)

Thus

$$\sum_{k=1}^{N_1} y_1[k] = \frac{N_1 X}{M - a_1}.$$

(11)

In practice, the input DC X is set as  $0 < X < M - a_1$ . So in order to make the right side of (11) an integer, the minimum nonzero solution of  $N_1$  has to be:

$$N_1 = \frac{M - a_1}{\lambda_1} \tag{12}$$

where  $\lambda_1$  is the greatest common divider of  $M-a_1$  and X. Since  $M-a_1$  is chosen as a prime number,  $M-a_1$  and X are always co-prime numbers. Hence,  $\lambda_1$  equals to 1.

$$N_1 = M - a_1 \tag{13}$$

If the process of (5)–(11) is repeated with the second EFM1, the sum of its output with a period  $N_2$  is obtained as:

$$\sum_{k=1}^{N_2} y_2[k] = \frac{\sum_{k=1}^{N_2} e_1[k]}{M - a_2}.$$

(14)

If the relationship between the sequence length of the first and second stages is:

$$N_2 = K_1 N_1 \tag{15}$$

(14) becomes

$$\sum_{k=1}^{N_2} y_2[k] = \frac{K_1 \sum_{k=1}^{N_1} e_1[k]}{M - a_2}.$$

(16)

Since  $e_1$  is periodic with a sequence length  $N_1$  [16], and recalling (13),

$$\sum_{k=1}^{N_1} e_1[k] = (M - a_1) \cdot mean(e_1). \tag{17}$$

On substitution of (17) into (16), a clearer expression is obtained:

$$\sum_{k=1}^{N_2} y_2[k] = \frac{K_1 \cdot (M - a_1) \cdot mean(e_1)}{M - a_2}.$$

(18)

The minimum solution of  $K_1$  in (18) is

$$K_1 = \frac{M - a_2}{\lambda_2} \tag{19}$$

where  $\lambda_2$  is the greatest common divider of  $M - a_2$  and  $(M-a_1) \cdot mean(e_1)$ . Substituting (13) and (19) into (15), the sequence length of the second stage is:

$$N_2 = \frac{(M - a_1)(M - a_2)}{\lambda_2}. (20)$$

If  $M - a_1$  and  $M - a_2$  are co-prime numbers, the greatest common divider of  $M - a_2$  and  $(M - a_1)mean(e_1)$  is 1. Thus the maximum sequence length for  $y_2$  is obtained as:

$$N_{2 max} = (M - a_1)(M - a_2). (21)$$

Continuing in this manner, the sequence length of the ith effective stage EFM1 in an lth order MASH modulator is:

$$N_i = \frac{(M - a_1)(M - a_2)...(M - a_i)}{\lambda_i}$$

(22)

where  $i \in \{1, 2, 3, ..., l\}$ , and  $\lambda_i$  is the maximum common divider of  $M - a_i$  and  $(M - a_1)(M - a_2)...(M - a_{i-1})mean(e_{i-1})$ . Note that when i = 1,  $mean(e_0) = X$  and  $M - a_0 = 1$ .

If  $\{(M-a_1), (M-a_2),...,(M-a_i)\}$  are co-prime numbers,  $\lambda_i=1$ . Thus the maximum sequence length of the ith stage EFM1 is:

$$N_{i\_max} = (M - a_1)(M - a_2)...(M - a_i).$$

(23)

As seen in Fig. 1, the output of the MASH modulator is obtained by simply summing and/or subtracting the output of each EFM1. Hence, the period of the MASH DDSM is the least common multiple of the sequence length of each stage:

$$N = \frac{(M - a_1)(M - a_2)...(M - a_{i-1})}{\lambda}$$

(24)

where  $\lambda$  is the least common multiple of  $\{\lambda_1, \lambda_2, ..., \lambda_l\}$ . When  $\{M_1, M_2, ..., M_l\}$  are co-prime numbers,  $\lambda$  becomes 1. Thus the maximum sequence length is:

$$N_{max} = (M - a_1)(M - a_2)...(M - a_l).$$

(25)

**Theorem 2.** The modulator output depends only on the first stage EFM1.

*Proof.* As seen in Fig. 1, at the output of the last adder,

$$v_{l-1}[1] = y_{l-1}[1] + y_l[1] - y_l[0]$$

(26)

$$v_{l-1}[2] = y_{l-1}[2] + y_l[2] - y_l[1]$$

(27)

:

$$v_{l-1}[N] = y_{l-1}[N] + y_l[N] - y_l[N-1]$$

(28)

where N is assumed as the sequence length of the MASH delta-sigma modulator. Adding all of the above equations yields:

$$\sum_{k=1}^{N} v_{l-1}[k] = \sum_{k=1}^{N} y_{l-1}[k] + \sum_{k=1}^{N} y_{l}[k] - \sum_{k=0}^{N-1} y_{l}[k].$$

(29)

Since the modulator sequence length, N, is a multiple of the period of any single stage,  $N_i$ , it follows that

$$\sum_{k=1}^{N} y_l[k] = \sum_{k=0}^{N-1} y_l[k]. \tag{30}$$

Thus:

$$\sum_{k=1}^{N} v_{l-1}[k] = \sum_{k=1}^{N} y_{l-1}[k]. \tag{31}$$

Similarly, the output of each of the other adders is obtained:

$$\sum_{k=1}^{N} v_{l-2}[k] = \sum_{k=1}^{N} y_{l-2}[k]$$

(32)

:

$$\sum_{k=1}^{N} v_2[k] = \sum_{k=1}^{N} y_2[k] \tag{33}$$

$$\sum_{k=1}^{N} y[k] = \sum_{k=1}^{N} y_1[k] \tag{34}$$

By combining with (11), the right-hand side of (34) may be expressed as:

$$\sum_{k=1}^{N} y_1[k] = K \sum_{k=1}^{N_1} y_1[k] = K \cdot N_1 \cdot \frac{X}{M - a_1}$$

(35)

where  $N_1$  is the sequence length of  $y_1$ , K is an integer and  $N = K \cdot N_1$ . By substituting (35) into (34), the average value of the MASH DDSM output y is determined as:

$$mean(y) = \frac{\sum_{k=1}^{N} y[k]}{N} = \frac{\sum_{k=1}^{N} y_1[k]}{K \cdot N_1} = \frac{X}{M - a_1}.$$

(36)

To sum up, the average value of the output is controlled only by the value  $M-a_1$  in the first stage EFM1 and is independent of other stages.

## 4 The Simulation Results

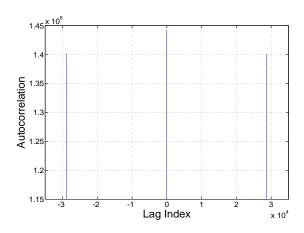

All of the models of the EFM1 and MASH DDSM are built and simulated in **Simulink**. The sequence length of the MASH DDSM is determined using the autocorrelation function [9]. As shown in Fig. 4, the sequence length of a 5-bit MASH 1-1-1 of the proposed form is  $28768 = (M-a_1) \cdot (M-a_2) \cdot (M-a_3)$  shown in Table 2. The sequence length of the HK-MASH and the proposed MASH are compared in Table 3. The sequence length of the proposed structure is greater and hence preferable. A longer sequence length means the noise spur is further out of the required modulation spectrum.

Figure 4: The autocorrelation result for the 5-bit proposed MASH 1-1-1.

Table 3: A comparison of the sequence lengths for the HK-MASH and proposed MASH.

| Word length | HK-MASH               | Proposed              | Difference            |

|-------------|-----------------------|-----------------------|-----------------------|

| 8 bit       | $15.81 \times 10^{6}$ | $16.39 \times 10^{6}$ | $+0.58 \times 10^{6}$ |

| 9 bit       | $131.87 \times 10^6$  | $133.17 \times 10^6$  | $+1.3 \times 10^{6}$  |

| 10 bit      | $1.06 \times 10^{9}$  | $1.07 \times 10^{9}$  | $+10 \times 10^{6}$   |

| 11 bit      | $8.48 \times 10^9$    | $8.55 \times 10^{9}$  | $+70 \times 10^{6}$   |

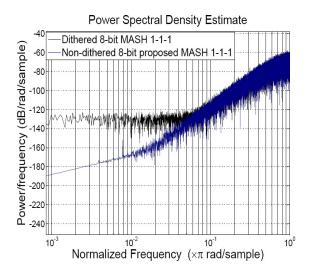

The power spectral density [22] of the 8-bit proposed MASH 1-1-1 and a dithered 8-bit MASH 1-1-1 is compared in Fig. 5. The proposed MASH has a better low-frequency noise floor than the classic MASH DDSM. Thus, it is a recommended structure.

Figure 5: The power spectral density of the dithered classic MASH DDSM and non-dithered proposed MASH.

### 5 Conclusion

A novel structure for the MASH digital delta-sigma modulator is proposed. It produces a very large sequence length and this is compared with that of the HK-MASH. The predicted sequence length of the proposed MASH DDSM is validated by simulation.

The power spectral density spectrum confirms that the proposed modulator architecture is more effective than the dithering method at moving noise from the lower frequencies, though dithering is one of the most effective existing methods for improving the noise performance.

The effect of the structure of the EFM1 is investigated in the paper. In particular, the effect of the value of  $M-a_i$  in the MASH digital delta-sigma modulator (DDSM) is explored. It is found that the output of the MASH modulator is only dependent on the structure of the first stage EFM1 and independent of the others. The expression for the sequence length of the EFM1 of each stage and the MASH DDSM are derived. The condition to yield the maximum modulator period is also given.

# Acknowledgement

The authors also would like to acknowledge Dr. Zhipeng Ye, University College Cork, for the valuable discussions.

### References

- [1] Gu, R., Ramaswamy, S., "Fractional-N Phase Locked Loop Design and Applications," *Proc. The 7th International Conference on ASIC*, Guilin, China, pp. 327–332, 10/07

- [2] Ye, Z., Chen, W., Kennedy, M. P., "A novel dual-loop multi-phase frequency synthesizer," Proc. European Conference on Circuit Theory and Design, Seville, Spain, pp. 567–570, 8/07

- [3] Xu, T., Ye, Z., Kennedy, M. P., "Mathematical Analysis of Injection-Locked Frequency Dividers," Proc. International Symposium on Nonlinear Theory and its Applications, Bologna, Italy, pp. 639– 642, 9/06

- [4] Ye, Z., Xu, T., Kennedy, M. P., "Locking Range Analysis for Injection Locking Frequency Dividers," Proc. International Symposium on Circuits and Systems, Island of Kos, Greece, pp. 4070–4073, 5/06

- [5] Christoffersen, C. E., Condon, M., Xu, T., "A New Method for the Determination of the Locking Range of Oscillators," Proc. European Conference on Circuit Theory and Design, Seville, Spain, pp. 575–578, 8/07

- [6] Xu, T., Condon, M., "An effective method for the determination of the locking range of an Injection-Locked Frequency Divider," Proc. Emerging Trends in Wireless Communications, Dublin, Ireland, pp. 47–50, 4/08

- [7] Xu, T., Condon, M., "Accurate Simulation of the Devil's Staircase of an Injection-Locked Frequency Divider," Proc. International Conference on Scientific Computing in Electrical Engineering, Espoo, Finland, pp. 105–106, 9/08

- [8] Reddy, A., "Noise Shaping with Sigma Delta Modulators in Fractional-N Synthesizers," Proc. IEEE Intl. Workshop on Radio-Frequency Integration Technology, Singapore, pp. 329–332, 12/07

- [9] Borkowski, M. J., Riley, T. A. D., Häkkinen, J., Kostamovaara, J., "A Practical Δ – Σ Modulator Design Method Based on Periodical Behavior Analysis," *IEEE Trans. on Circuits and Systems-II: Express Briefs*, V52, N10, pp. 626–630, 10/05

- [10] Kozak, M., Kale, İ., "Rigorous Analysis of Delta-Sigma Modulators for Fractional-N PLL Frequency Synthesis," *IEEE Trans. on Circuits and Systems-I:* Regular Papers, V51, N6, pp. 1148-1162, 6/04

- [11] Ouzounov, S., Hegt, H., Roermund, A. V., "Sigma-Delta Modulators Operating at a Limit Cycle," *IEEE Trans. on Circuits and Systems-II: Express Briefs*, V53, N5, pp. 399-403, 5/06

- [12] Reefman, D., Reiss, J., Janssen, E., Sandler, M., "Description of limit cycles in sigma-delta modulators," *IEEE Trans. on Circuits and Systems-I: Regular Papers*, V52, N6, pp. 1211-1223, 6/05

- [13] Reiss, J., Sandler, M., "Detection and removal of limit cycles in sigma delta modulators," accepted for IEEE Trans. on Circuits and Systems-I: Regular Papers, 2008.

- [14] Pamarti, S., Welz, J., Galton, I., "Statistics of the Quantization Noise in 1-Bit Dithered Single-Quantizer Digital Delta-Sigma Modulators," *IEEE Trans. on Circuits and Systems-I: Regular Papers*, V54, N3, pp. 492-503, 3/07

- [15] Pamarti, S., Galton, I., "LSB Dithering in MASH Delta-Sigma D/A Converters," *IEEE Trans. on Cir*cuits and Systems-I: Regular Papers, V54, N4, pp. 779-790, 4/07

- [16] Hosseini, K., Kennedy, M. P., "Maximum Sequence Length MASH Digital Delta-Sigma Modulators," *IEEE Trans. on Circuits and Systems-I: Regular Pa*pers, V54, N12, pp. 2628-2638, 12/07

- [17] Hosseini, K., Kennedy, M. P., "Mathematical Analysis of a Prime Modulus Quantizer MASH Digital Delta-Sigma Modulator," *IEEE Trans. on Circuits and Systems-II: Express Brief*, V54, N12, pp. 1105-1109, 12/07

- [18] Hosseini, K., Kennedy, M. P., "Mathematical analysis of digital MASH delta-sigma modulator for fractional-N frequency synthesizers," Proc. IEEE Ph. D. Research in Microelectronics and Electronics, Otranto (Lecce), Italy, pp. 309-312, 6/06

- [19] Hosseini, K., Kennedy, M. P., McCarthy, C., "Calculation of Sequence Lengths in MASH 1-1-1 Digital Delta Sigma Modulators with a Constant Input," Proc. IEEE Ph. D. Research in Microelectronics and Electronics, Bordeaux, France, pp. 13-16, 6/07

- [20] Crandall, R. E., Pomerance, C., *Prime numbers: a computational perspective*, Springer, 2001.

- [21] Borkowski, M. J., Kostamovaara, J., "Spurious Tone Free Digital Delta-Sigma Modulator Design for DC Inputs," Proc. IEEE International Symposium on Circuits and Systems, Kobe, Japan, pp.5601-5604, 5/05

- [22] Oppenheim, A. V., Schafer, R. W., Discrete-Time Signal Processing, Upper Saddle River, NJ: Prentice-Hall, 1999.