# A Ka-Band CMOS Voltage Controlled Oscillator for High Speed Wireless Communication

Zhe-Yang Huang

*Abstract* — A 32.09GHz-34.59GHz Ka-Band CMOS Voltage-Controlled Oscillator (VCO) is designed for high speed wireless communication. The oscillator providing a center frequency of 33.34GHz and is implemented in 90nm Logic CMOS Technology. The oscillator core consumes 4.39mW through 1.0V supply voltage and the total chip area is 0.29mm<sup>2</sup> including pads and by-pass capacitors. A tuning range of 2.5GHz (32.09GHz-34.59GHz) with maximum control voltage of 1.0V can be achieved. And the phase noise is -85.2dBc/Hz at 1MHz offset from the center oscillator frequency. The calculated figure-of-merit (FOM) is -171.9dBc/Hz.

*Index Terms* — CMOS, Voltage-Controlled Oscillator, VCO, Ka-Band.

## I. INTRODUCTION

In convention, the millimeter wave radio circuits are implemented in Gallium Arsenide (GaAs) or Silicon Germanium (SiGe) technologies [1-4]; but those technologies are not easy to integrate with baseband circuits and the cost is also high. Due to the CMOS technology is rapidly progressing, CMOS technology is becoming a good choice for millimeter wave components design. This paper is presenting a Ka-Band CMOS voltage controlled oscillator (VCO) for high speed wireless communication applications. VCO is a crucial component in wireless receiver system, and the most important performance is the phase noise which influences the sensitivity of the wireless communication system.

#### II. CIRCUIT IMPLEMENTATION

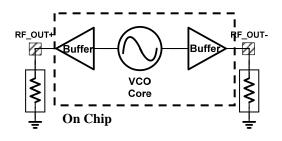

Voltage controlled oscillator is implemented as Figure 1; including VCO core and buffer which is for measurement purpose. The output of the VCO is differential sinusoidal signal which means the phase of the signal is different from  $180^{\circ}$ . The core of the oscillator contributes continuous sinusoid millimeter wave to provide the mixing LO signals. And the buffer contributes the 50 Ohm impedance for measurement instruments. In this design, the VCO core and buffers are all designed on chip.

Institute (ITRI), Hsin-Chu, CO 31040, Taiwan. (phone: 886-3-5914759; fax: 886-3-5820226; e-mail: maverick\_huang@itri.org.tw).

Figure1 Oscillator for Measurement Purpose

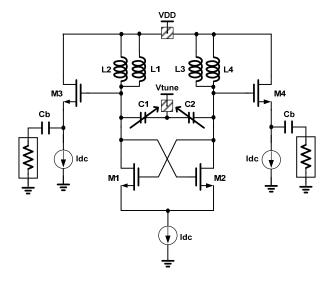

The circuit schematic of the Ka-Band voltage controlled oscillator is shown in Figure 2.  $M_1$ ,  $M_2$  are the cross coupled pair;  $L_1$ ,  $L_2$ ,  $L_3$ ,  $L_4$ ,  $C_1$ ,  $C_2$  are consisting of the LC-Tank; and  $M_3$ ,  $M_4$  are the source follower. NMOS cross coupled pair  $M_1$ ,  $M_2$  contributes the negative  $g_m$  for the VCO core and the condition of oscillation is expressed in equation (1). The LC-Tank determines the center frequency  $F_c$  of the oscillator which is expressed in equation (2). The capacitor  $C_1$ ,  $C_2$  are voltage controlled capacitors; the capacitance will be varied by the control voltage. Therefore, the center frequency  $F_c$  of the oscillator will also be changed. In Standard Logic CMOS 90nm process, the top metal is not ultra thick metal (UTM) and there are no standard inductors in foundry design kit (FDK). Therefore an accurate electro-magnetic (EM) simulation for inductor design is necessary and important.

$$g_m > \frac{2}{R_p} \tag{1}$$

$$F_{c} = \frac{1}{2\pi\sqrt{L_{1} \parallel L_{2}(C_{1} + C_{p})}}$$

(2)

Figure2 Circuit of Voltage Controlled Oscillator

Manuscript received July 11, 2010. This work was supported in part by the Industrial Technology Research Institute (ITRI) in Hsin-Chu, Taiwan. Zhe-Yang Huang, Author is with Industrial Technology Research

Proceedings of the World Congress on Engineering and Computer Science 2010 Vol II WCECS 2010, October 20-22, 2010, San Francisco, USA

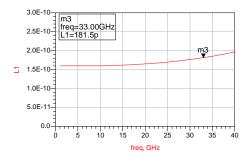

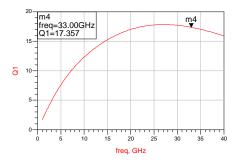

The simulation results from electro-magnetic tool are illustrated in Fig. 3 and Fig. 4. The equivalent inductance of the parallel inductor is shown in Figure 3; the inductance at 33GHz is 181.5pH. And the quality factor (Q-Factor) is 17.35 and which is shown in Figure 4.

Figure3 Equivalent Inductance of Load

Figure4 Quality Factor of Load

## **III. EXPERIMENT RESULTS**

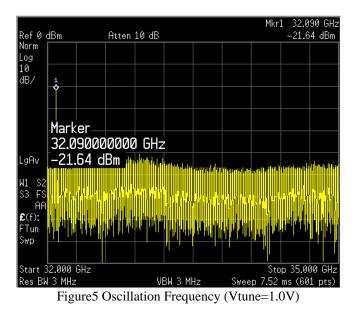

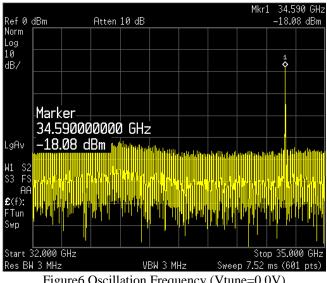

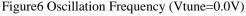

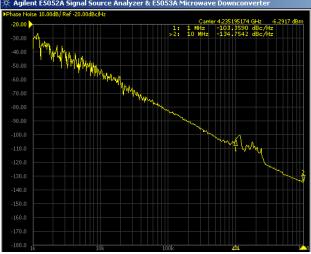

The core circuit of VCO draws 4.39mA current while consuming 4.39mW power through 1.0V supply voltage. The spectrum measurement results illustrated in Fig. 5 to Fig. 6; the oscillator frequency can be varied from 32.09GHz to 34.59GHz by 1.0V tuning controlled voltage; and this VCO has 2.50GHz tuning range. The output power of the VCO at 32.09GHz is -21.64dBm and at 34.59GHz is -18.08dBm. Phase noise of Ka-Band VCO is not able to measure directly in Signal Source Analyzer, thus down-conversion of the oscillated signal is necessary. There are two helpful solutions, one is dividing the frequency, and the other is mixing the mm-wave frequency. In this case, we choose to divide the mm-wave signal which is shown in Fig. 7. The divisor is set as 8, and the measurement frequency is down-converted into 4.235GHz. In Figure 7, the VCO oscillated signal will go through a pre-amplifier in order to make the divider sense the weak signal from VCO. The measured phase noise is -103.3dBc/Hz at 1MHz offset and -134.7dBc/Hz at 10MHz offset which is illustrated in Figure 8. But the phase noise is measured at 4.235GHz; it should be compensated 18.06dB which is expressed in equation (3). After compensating, the actual phase noise at 33.88GHz is -85.24dBc/Hz at 1MHz offset and -116.64dBc/Hz at 10MHz offset. The figure-of-merit (FOM) is expressed in equation (4) where  $L(\Delta f_{offset})$  is phase noise at  $\Delta f_{offset}$  frequency offset,  $f_o$  is the center frequency of the oscillator, PDC is the power

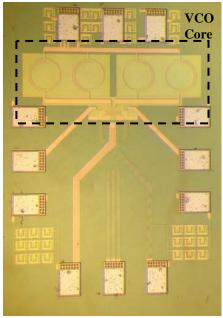

dissipation of the oscillator. Finally, the calculated FOM is -171.90dB/Hz. Table1 is the performance conclusions of this voltage controlled oscillator; and Table2 is the performance comparisons with some recent works. The micro-photography of the chip is shown in Fig. 9. The whole chip size including all pads and all bypass capacitors is 0.45mm X 0.64mm and total area is 0.29mm<sup>2</sup>.

$$PN_{comp} = 20 * \log(8) = 18.06 dB \tag{3}$$

$$FoM = L(\Delta f_{offset}) - 20 * \log(\frac{f_o}{f_{offset}}) + 10 * \log(\frac{P_{DC}}{1mW})$$

(4)

Figure7 Down-Conversion for Phase Noise Measurement

Proceedings of the World Congress on Engineering and Computer Science 2010 Vol II WCECS 2010, October 20-22, 2010, San Francisco, USA

Figure8 Phase Noise @ 1MHz Offset from Center Freq.

Figure9 Micro-Photography of Chip

## IV. CONCLUSIONS

A 1V 4.39mW 32.09GHz-34.59GHz CMOS Voltage Controlled Oscillator (VCO) is designed and implemented in 90nm Logic CMOS technology for mm-wave high speed wireless communication system. The VCO is offering a center frequency of 33.34GHz and the tuning range of 2.5GHz (32.09GHz-34.59GHz). The oscillator core consumes 4.39mW through 1.0V supply voltage and the total area is 0.29mm<sup>2</sup>. The phase noise is -85.2dBc/Hz at 1MHz offset and -116.6dBc/Hz at 10MHz offset from the center frequency. The calculated figure-of-merit (FOM) is -171.90dB/Hz.

| TABLET FEHOIMAICE COlleusions |                                     |  |  |  |

|-------------------------------|-------------------------------------|--|--|--|

| Technology                    | 90nm Logic CMOS                     |  |  |  |

| Supply Voltage                | 1.0V                                |  |  |  |

| Oscillation Freq.             | 32.090 GHz ~ 34.590 GHz             |  |  |  |

| Tuning Range                  | 2.50 GHz                            |  |  |  |

| Output Power<br>(w/i buff.)   | -21.64dBm ~ -18.08dBm               |  |  |  |

| Phase Noise<br>(@1MHz offset) | -82.1dBc/Hz ~ -87.5dBc/Hz           |  |  |  |

| Power Dissipation             | 4.39 mW                             |  |  |  |

| FOM                           | -171.90 dB                          |  |  |  |

| Chip Area                     | 0.29mm <sup>2</sup> [0.45 X 0.64mm] |  |  |  |

TABLE1 Performance Conclusions

#### ACKNOWLEDGMENT

This work was supported by Industrial Technology Research Institute (ITRI) under Project 9301XS2E10.

#### REFERENCES

- [1] A. Kurdighlian, M. Mokhtari, C. H. Fields, M. Wetzel, M. Sokolich, M. Micovic, S. Thmas, III, B. Shi and M. Sawins. "40 GHz fully integrated and differential monolithic VCO with wide tuning range in AlInAs/InGaAs HBT", IEEE GaAs Symp. Dig., Jun. 2001, pp. 129-132.

- [2] B. Piernas, K. Nishikawa, T. Nakagawa and K. Araki, "A compact and low-phase-noise Ka-band pHEMT-based VCO", IEEE Transaction on Microwave Theory and Techniques, vol. 51, pp.778-783, Mar. 2003.

- [3] Y.-J. E. Chen, W.-M. L. Kuo, J. Lee, J. D. Cressler, J. Laskar, and G. Freeman, "A low power –Ka-band SiGe HBT VCO using line inductors", IEEE Radio Frequency Integrated Circuits (RFIC) Symp. Dig., Jun. 2004, pp. 587-590.

- [4] J. Hilsenbeck, F. Lenk, W. Heninrich, and J. Wurfl, "Low phase noise MMIC VCOs for Ka-band applications", IEEE GaAs Symp. Dig., Jun. 2003, pp. 223-226.

- [5] N. Fong, J. Kim, J. O. Plouchart, N. Zamdmer, D. Liu, L. Wagner, C. Plett, and G. Tarr, "A low-voltage 40-GHz complementary VCO with 15% frequency tuning range in SOI CMOS technology", IEEE Journal of Solid-State Circuits, vol. 39, no. 5, pp. 841-846, May 2004.

| TABLE2 Ferrormance Comparisons |            |            |              |            |             |          |  |  |

|--------------------------------|------------|------------|--------------|------------|-------------|----------|--|--|

|                                | Process    | Osc. Freq. | Output Power | P.N. @1MHz | Power Diss. | FOM      |  |  |

|                                |            | [GHz]      | [dBm]        | [dBc/Hz]   | [mW]        | [dBc/Hz] |  |  |

| [1]                            | InGaAs HBT | 39.0       | +2           | -95.0      | 42.0        | -170.6   |  |  |

| [2]                            | GaAs pHEMT | 28.3       | +11.8        | -102.0     | 80.0        | -172.0   |  |  |

| [3]                            | SiGe HBT   | 33.0       | -17.0        | -99.0      | 3.7         | -183.7   |  |  |

| [4]                            | GaAs       | 34.0       | +4.0         | -108.0     | 157.5       | -176.7   |  |  |

| [5]                            | CMOS SOI   | 40.0       | -8.0         | -90.0      | 11.3        | -171.5   |  |  |

| This Work                      | CMOS       | 33.34      | -18.0        | -85.2      | 4.4         | -171.9   |  |  |

**TABLE2** Performance Comparisons