# **PVT Insensitive Reference Current Generation**

Suhas Vishwasrao Shinde

Abstract— In this paper, supply, process & temperature compensated, low voltage current reference for CMOS integrated circuits is presented. To minimize production cost, it uses no BJTs, external components or trimming procedures. This circuit is designed in Intel-22nm process and evaluated by computer simulations. The circuit behaviour is supported by theoretical expressions and is in agreement with simulation results. A comparison with most current references in the literature shows considerable tolerance improvement. Simulation results show PVT tolerance of +/-10% and 1 $\sigma$  standard deviation of 5uA at mean of 82uA. An autonomous, all MOS, low voltage & process technology independent features make it suitable for advanced sub micron processes like 14nm, 10nm & beyond.

*Keywords*— CMOS integrated circuits, current reference, bandgap reference, process and temperature compensation, sub threshold, weak inversion, strong inversion, PTAT, CTAT, BGR.

### I. INTRODUCTION

An ideal current reference circuit should be autonomous and should be used locally per analog block from modularity point of view. This avoids long reference current distribution network and associated issues of IR drop, noise coupling and current mirroring mismatch. A classical way of current reference generation is by a resistor as current defining element [16]. This requires precise bandgap reference voltage and off-chip precision resistor which consumes I/O pin. It also involves a feedback loop hence may break in to oscillations if not meeting sufficient phase margin criteria. Although this current reference is very accurate it increases the system cost. Several integrated current reference circuits have been reported in the past which avoids explicit voltage reference and external components. However these current references either compensate for temperature or for process and not for both. In this paper, MOS reference current circuit has proposed which has very low sensitivity for supply, process and temperature variations. Further it enables modular design approach for large systems because it does not require bandgap reference (BGR) circuit, regulator or external components. This architecture exploits the sub threshold region properties of MOSFET to generate reference current. This sub threshold region operation allows use of low supply voltage (~1V).

Manuscript received December 17, 2013; revised January 30, 2014. Suhas V. Shinde is Sr. Mixed Signal IC Design Engineer with Intel Mobile Communications GmbH, Neubiberg 85579, Germany. (phone: +498999885321131; e-mail: suhas.v.shinde@intel.com). Low voltage operation is gaining importance for advanced sub micron processes due to devices shrinking down and becoming more fragile with reduced electrical stress limit.

The proposed scheme of reference current generation is realized by summation of process & supply compensated proportional to absolute temperature (PTAT) & complementary to absolute temperature (CTAT) currents. Precise reference current is generated by adjusting negative temperature coefficient of CTAT current such that it ideally cancels positive temperature coefficient of PTAT current. This architecture is feed forward system and hence no stability issue arises. All MOS implementation, low voltage operation and process technology independent operation makes it suitable for advanced sub micron processes like 14nm, 10nm and onwards.

This paper is organised in to 6 sections. Section II describes theory and circuit of supply and process immune PTAT current generation. Section III explains theory and circuit of supply and process immune CTAT current generation. Section IV develops new reference current generation circuit and section V reports simulation results from Intel-22nm process, testing theory and validating proposed reference current circuit. Finally section VI gives concluding remark.

#### II. PTAT CURRENT GENERATION

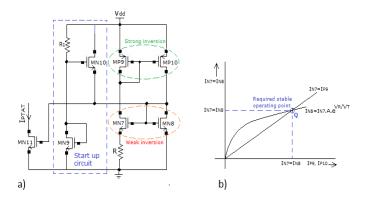

In this section, a standard voltage reference circuit [9] is described as supply & process insensitive PTAT current generating circuit. A PTAT current circuit is as shown in fig. 1a). Here devices MP9 and MP10 are operated in strong inversion whereas MN7 and MN8 are operated in weak inversion.

Fig. 1 a) PTAT circuit and [9] b) start-up operating points.

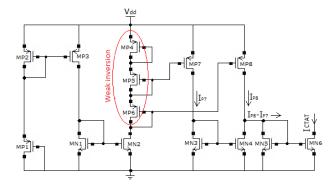

Fig. 2. CTAT current circuit [8].

$$I_{PTAT} = V_{REF} / R$$

Therefore

$$I_{PTAT} = \frac{\eta V_T}{R} ln(\frac{S_{N7}}{S_{N8}}, \frac{S_{P10}}{S_{P9}})$$

$$I_{PTAT} = \frac{\eta KT}{R} ln(\frac{S_{N7}}{S_{N8}}, \frac{S_{P10}}{S_{P9}})$$

(1)

Since  $V_T = KT/q$

Where the slope,

$$m = \frac{\eta}{R} \frac{K}{q} ln(\frac{S_{N7}}{S_{N8}}, \frac{S_{P10}}{S_{P9}})$$

(2)

Where K= Boltzmann constant

q = Electronic charge

**η** ~ 1

The slope or temperature coefficient of CTAT current can be adjusted through design parameter SN7, SN8, SP10, SP9 and resistor R.

The circuit in fig. 1 a) has two stable operating points; First, where no current flows in any branch of circuit and PTAT voltage is zero & second, where IN7 is equal to IN8. The circuit is brought up to this 2nd stable operating point by start up circuit comprised of MN9, MN10 & resistor R1.

## III. CTAT CURRENT GENERATION

This section presents supply and process insensitive CTAT current generation based on subtraction of two currents [8]. It uses natural variation of two currents to cancel out variation in the difference current. The current subtraction is such that their difference is non-zero but their process coefficient is the same. Hence their variation across process gets cancelled. Although process coefficient is made zero (theoretically!), variation with respect to another independent variable temperature exist. The observed temperature coefficient of current is negative giving rise to CTAT current. The underlying theory and model of process compensation of current for circuit in fig. 2 is as follows.

$I_{P8} \approx \beta z_8 (V_{GS8} - V_{TP})^2$  and

Hence,

$$\begin{split} I_{P9} &= \frac{\beta_{P9}}{2} (V_{GS9} - V_{TP})^2 \\ I_{P10} &= \frac{\beta_{P10}}{2} (V_{GS10} - V_{TP})^2 \\ I_{N7} &= I_0 \frac{W_{N7}}{L_{N7}} e^{(V_{GS7} - V_{TN})/\eta V_T} \\ I_{N8} &= I_0 \frac{W_{N8}}{L_{N8}} e^{(V_{GS8} - V_{TN})/\eta V_T} \end{split}$$

Designing,  $\beta_{N8} = A \beta_{N7} =>$

$$\frac{W_{N8}}{L_{N8}} = A \frac{W_{N7}}{L_{N7}}$$

Therefore,

$$I_{N8} = I_0 A \frac{W_{N7}}{L_{N7}} e^{(V_{GS8} - V_{TN})/\eta V_T}$$

$$I_{N8} = I_0 A \frac{W_{N7}}{L_{N7}} e^{(V_{GS7} + V_R - V_{TN})/\eta V_T}$$

since  $V_{GS8} = V_{GS7} + V_R$

Therefore,

$$I_{N8} = I_{0} A \frac{W_{N7}}{L_{N7}} e^{V_{R}/\eta V_{T}} e^{(V_{GS7}-V_{TN})/\eta V_{T}}$$

$$I_{N8} = I_{0} \frac{W_{N7}}{L_{N7}} e^{(V_{GS7}-V_{TN})/\eta V_{T}} A e^{V_{R}/\eta V_{T}}$$

$$I_{N8} = I_{N7} A e^{V_{R}/\eta V_{T}}$$

Designing for  $\,{}^{I_{P10}\,=\,B\,I_{P9}}$  =>

Therefore,

$$V_{REF} = \eta V_T \ln(\frac{S_{N7}}{S_{N8}}, \frac{S_{P10}}{S_{P9}})$$

Where A=SN8/SN7, B=SP10/SP9

and

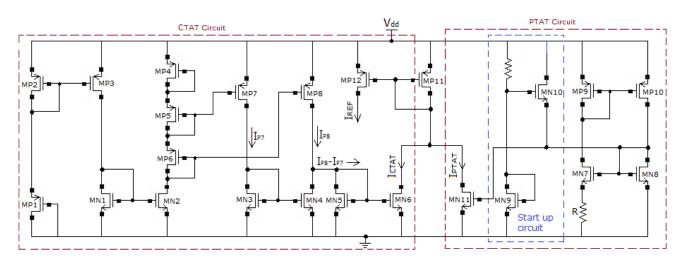

Fig. 3. Proposed reference current generation circuit.

(3)

$$I_{P7} \approx \beta z_7 (V_{GS7} - V_{TP})^2$$

Where reference current,

For reference current variation with respect to process to be zero,

$$\frac{\partial I_{\text{REF}}}{\partial P} = 0 \implies \frac{\partial I_{\text{P8}}}{\partial P} = \frac{\partial I_{\text{P7}}}{\partial P}$$

Where

$$\frac{\partial I_{P8}}{\partial P} = z_8 (V_{GS8} - V_{TP})^2 \frac{\partial \beta}{\partial P} - 2\beta z_8 (V_{GS8} - V_{TP}) \frac{\partial V_{TP}}{\partial P} \quad \text{and}$$

$$\frac{\partial I_{P7}}{\partial P} = z_7 (V_{GS7} - V_{TP})^2 \frac{\partial \beta}{\partial P} - 2\beta z_7 (V_{GS7} - V_{TP}) \frac{\partial V_{TP}}{\partial P}$$

Therefore

$$z_{8}(V_{GS8}-V_{TP})^{2}\frac{\partial\beta}{\partial P} = -2\beta z_{7}(V_{GS7}-V_{TP})\frac{\partial V_{TP}}{\partial P} \text{ and}$$

$$z_{7}(V_{GS7}-V_{TP})^{2}\frac{\partial\beta}{\partial P} = -2\beta z_{8}(V_{GS8}-V_{TP})\frac{\partial V_{TP}}{\partial P}$$

Therefore

$$\frac{z_{8}(V_{GS8}-V_{TP})^{2}}{z_{7}(V_{GS7}-V_{TP})^{2}} = \frac{z_{7}(V_{GS7}-V_{TP})}{z_{8}(V_{GS8}-V_{TP})}$$

$$=> (\frac{z_{8}}{z_{7}})^{2} = \frac{(V_{GS7}-V_{TP})^{3}}{(V_{GS8}-V_{TP})^{3}}$$

$$=> \frac{z_{8}}{z_{7}} = \left(\frac{V_{GS7}-V_{TP}}{V_{GS8}-V_{TP}}\right)^{\frac{3}{2}}$$

$$=> \frac{z_{8}}{z_{7}} = \left(\frac{a_{VTP}-V_{TP}}{b_{VTP}-V_{TP}}\right)^{\frac{3}{2}}$$

Where  $V_{GS7} = aV_{TP}$  and  $V_{GS8} = bV_{TP}$

$$\frac{z_8}{z_7} = \left(\frac{a-1}{b-1}\right)^{3/2}$$

For b=3 and a=2,  $z_8/z_7 = 0.3535 \Rightarrow z_7 = (2.84)z_8$

Thus choosing MP7 size 2.84 times MP8 creates zero process coefficient (ZPC). The process insensitive difference current is immune against supply variation as well because subtraction operation of  $I_{P7}$  and  $I_{P8}$  cancels out their variation partially. Although process and supply variation is cancelled the variation due to other independent variable called temperature still exist which exhibits CTAT behaviour.

#### IV. IREF CURRENT GENERATION

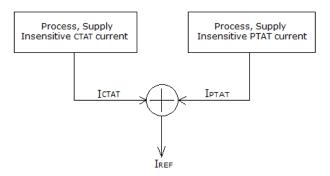

The basic principle of the reference current generation is illustrated in fig. 4 where supply & process insensitive PTAT & CTAT currents are added. Fig. 3 shows complete circuit schematic of current reference, developed by combining PTAT & CTAT circuits from sections II & III respectively. It's all MOSFET integrated circuit design with 1V supply. The negative temperature coefficient of CTAT current can be adjusted to match the positive temperature coefficient of PTAT current to nil temperature variation. From equation (2) design parameters SN7, SN8, SP10, SP9 and R can be tuned to adjust negative temperature coefficient of CTAT current. The design equations are solved and circuit is optimized considering extremes of supply, process and temperature corners for minimum reference current variation.

Fig. 4. Basic principle of reference current generation.

The low voltage operation of this circuit is an advantage over prior art architectures which require 2.5V [7] and 3.5V [2] supply voltages. Some reported current reference circuits [6] involve feedback loops hence critical from stability point of view. This circuit has no stability issues being feedforward system.

## V. SIMULATION RESULTS

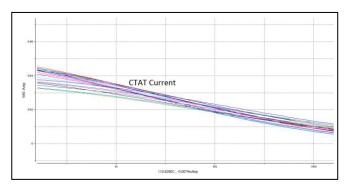

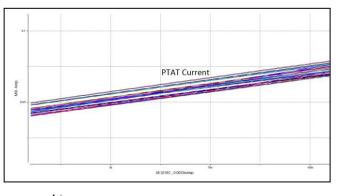

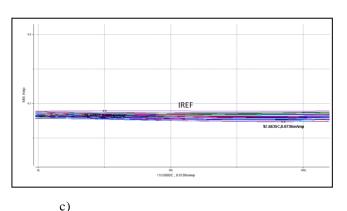

This current reference is designed in Intel-22nm process and simulation results are reported to test mathematical model and validate the design. Fig. 5 a) shows I-T characteristic curve of PTAT current generated by voltage reference circuit depicted in fig. 1 a). Fig. 5b) shows I-T characteristic curve of CTAT current generated by circuit architecture in fig. 2. The addition of these two currents results in to reference current characteristics as plotted in fig. 5c). The extreme PVT variation observed is +/- 10%. This tolerance is over temperature range of 0°C to 110°C, supply variation +/-5% and on-die calibrated resistor variation of +/- 5%. The PVT performance comparison of this current reference with prior published work in [4], [6] & [7] shows better results due to the fact that they do not address all variations together. The +/-10% tolerance is mainly attributed to non linearity of PTAT & CTAT currents with respect to temperature, partial compensation of CTAT current with respect to supply variation and small but finite variation of calibrated resistor. A word of caution to designers about SPICE simulations! Precaution has to be taken with respect to SPICE simulations since sub threshold region models may not be accurate for their process.

a)

b)

Fig. 5 a) PTAT current b) CTAT current and c) IREF current.

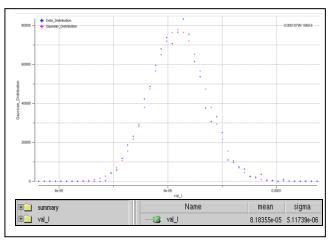

Fig. 6. Monte Carlo results showing normal Pdf with  $\mu{=}82uA$  and  $1\sigma$  SD = 5uA.

The incorrect modelling of weak inversion region tends to predict good results and hence silicon correlation becomes necessary. Finally Fig. 6 shows statistical simulation results for reference current under typical conditions, supply=1V, process = typical, and temperature = 50°C. Observed 1 $\sigma$  standard deviation for 1000 runs is 5uA at mean value of 82uA. This statistical spread,  $\sigma/\mu$  =0.06 is significantly lesser than reported results in [2].

## VI. CONCLUSION

This paper demonstrates an alternative approach of reference current generation with necessary mathematical expressions. It verifies approach through circuit simulations of current reference designed in Intel 22nm process. The proposed architecture provides immunity against supply, process and temperature variations. An autonomous nature makes it suitable for modular design style of large systems. This circuit is easy to use for biasing applications in analog circuits. An autonomous, low voltage, CMOS compatibility and process insensitive features make it suitable for advanced sub micron processes.

#### ACKNOWLEDGMENT

The author wishes to thank HIP, Intel Microelectronics, Penang for providing necessary access to tools and Intel 22nm process technology.

#### REFERENCES

- Yannis Tsividis, "Operation and Modeling of The MOS Transistor", Second Edition, Oxford University press, ISBN 0-19-569358-2.

- [2] Willy M. Sansen, Frank Opt Eynde, Michiel Steyaert, "A CMOS Temperature-Compensated Current Reference", IEEE Journal of Solid-State Circuits, vol. 23, No. 3, June 1988.

- [3] C.H. Lee and H.-J. Park, "All-CMOS temperature independent current reference", Electronics Letters, 4th July 1996, vol.32, No. 14.

- [4] Henri J. Oguey and Daniel Aebischer, "CMOS Current Reference without Resistance", IEEE Journal of Solid-State Circuits, vol. 32, No. 7, July 1997

- [5] C.Yoo, J. Park, "CMOS current reference with supply and temperature compensation", Electronics Letters, 6th December 2007, Vol 43, No.25

- [6] Zhao Zhe, Zhou Feng, Huang Shengzhuan, "All-CMOS temperature compensated current reference", Journal of Semiconductors, vol. 31, No. 6, June 2010

- [7] Franco Fiori, Paolo Stefano Crovetti, "A New Compact Temperature-Compensated CMOS Current Reference", IEEE Transactions on Circuits and Systems, vol. 52, No.11, November 2005

- [8] S. Tang, S. Narendra, and V. De, "Temperature and process invariant MOS-based reference current generation circuits for sub-1 V operation," in Proc. ISLPED'03, pp. 199–204.

- [9] E. Vittoz and J. Fellrath, "CMOS analog integrated circuits based on weak inversion operation," IEEE J. Solid-State Circuits, vol. SC-12, no.

3, pp. 224–231, Jun. 1977.I

- [10] I. M. Filanovsky and A. Allam, "Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS," IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 48, no. 7, pp. 876–884, Jul. 2001.

- [11] S. M. Sze, Physics of Semiconductor Devices. New York:Wiley, 1969.

- [12] Yoo C, Park J. CMOS current reference with supply and temperature compensation. Electron Lett, 2007, 43(25): 1422

- [13] Bendali A, Audet Y. A 1-V CMOS current reference with temperature and process compensation. IEEE Trans Circuits Syst I: Regular Papers, 2007, 54(7): 1424

- [14] H. Banba, H. Shiga, A. Umezawa, T. Miyaba, T. Tanzawa, S. Atsumi, and K. Sakui, "A CMOS band-gap reference circuit with sub 1 V operation," Symp. on VLSI Circuits, 228-229, Jun 1998.

- [15] E. Vittoz, "The design of high performance analog circuits on digital CMOS chips", IEEE Journal of Solid State Circuits, Vol. SC-20, No 3, pp. 657-665, June 1985.

- [16] P. R. GRAY and R. G. MEYER-"Analysis and design of analog integrated circuits" New York, Wiley 1977.