# An on-chip Low Drop-Out Voltage Regulator with 150mA Driving Capability

Lv Xiaopeng, Bian Qiang, Yue Suge

Abstract—To realize DC voltage conversion from 3.3V to 1.8V for SoC application, a fully on-chip Low Drop-Out (LDO) voltage regulator with 150mA driving capability is presented. Implemented in 0.18 $\mu$ m CMOS technology, the proposed LDO voltage regulator utilizes paralleled input differential pairs and current amplifiers to provide fast transient response, achieving 1.4 $\mu$ s settling time with transient variation less than 155mV.

*Index Terms*—Capacitor-less LDO; Frequency compensation; Transient response; Power supply rejection.

#### I. INTRODUCTION

As an essential building block of the power management system, the Low Drop-Out (LDO) voltage regulators based on feedback provide an accurate and stable voltage with corresponding load current. Recently, the off-chip output capacitor of several micro farads is eliminated for System on Chip (SoC) application [1]; however, the on-chip output capacitor is deceased to only several tens or hundreds of pico farads, degrading the stability and the transient response.

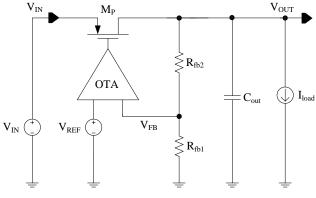

Fig. 1. Structure of on-chip LDO voltage regulator

The structure of fully on-chip LDO voltage regulators implemented in CMOS technology (Fig. 1) often uses the PMOS FET with common source connection as the pass transistor between the input and output voltages. An amplified error signal is fed back to the gate of the pass transistor through the feedback loop to respond to the load current while keeping the output voltage constant. Stability

Lv Xiaopeng is with Beijing Microelectronic Technology Institute, Beijing, China, working towards the Master degree. (Email: Xiaopeng\_Lv@163.com)

Bian Qiang and Yue Suge are engineers with Beijing Microelectronic Technology Institute, Beijing, China.

over the full range of load current and small output voltage variation during load current transient are the state-of-art of the on-chip LDO voltage regulators.

Several approaches have been introduced to on-chip LDO voltage regulator for SoC application. Lau *et al.* proposed advanced Q-reduction circuit with minimum load current of 100  $\mu$ A [2]; Milliken *et al.* adopted differentiator and current amplifier for stability and fast transient response [3]; Ho *et al.* employed active feedback and slew rate enhancement to minimize compensation capacitor and speed up transient response [4].

In this paper, an OTA based on paralleled differential input pairs and current amplifier is adopted to increase GBW and SR, speeding up the transient response; Miller compensation is employed to ensure loop stability with load current from  $100\mu$ A to 150mA. The proposed LDO voltage regulator with 100pF on-chip output capacitor provides 1.8V output voltage with 150mA driving capability. In section II, stability, transient response and power supply rejection characteristics of the proposed LDO voltage regulator are discussed. In section III, the static-state, dynamic-state and PSR characteristics are simulated and corresponding simulation results are summarized with comparisons. The conclusion is derived in section IV.

## II. THE PROPOSED LDO VOLTAGE REGULATOR

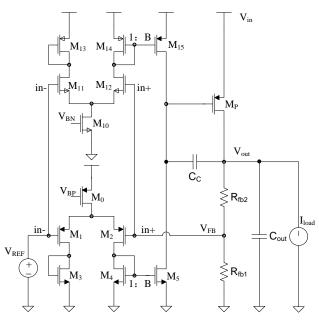

Fig. 2. Schematic of the proposed on-chip LDO voltage regulator

The transistor level implementation of proposed on-chip

Proceedings of the World Congress on Engineering and Computer Science 2011 Vol II WCECS 2011, October 19-21, 2011, San Francisco, USA

LDO voltage regulator is shown in Fig. 2. Transistors  $M_0-M_5$ and  $M_{10}-M_{15}$  forms the symmetrical OTA with paralleled input differential pairs, where B is the current gain. The PMOS FET  $M_P$  in common source connection is the pass transistor between the input and output voltage. The series feedback network composed of  $R_{fb1}$  and  $R_{fb2}$  provides the feedback signal  $V_{FB}$  to the non-inverting input of the OTA while the reference provides the signal  $V_{REF}$  to the inverting input of the OTA.

## A. Stability analysis

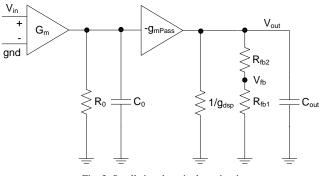

For stability analysis of the feedback loop, small signal equivalent circuit of the proposed on-chip LDO is shown in Fig. 3, where  $G_m$  is the transconductance of the paralleled input differential pairs,  $R_0$ ,  $C_0$  are the resistor and capacitor at the OTA output.  $C_{out}$  is the on-chip output capacitor at the output of the LDO voltage regulator.

Fig. 3. Small signal equivalent circuit

The small signal loop gain at low frequency can be given as bellow

$$LG = \frac{V_{fb}}{V_{in}} = A_{V_{o}OTA}A_{V_{o}P}$$

$$= G_{m}R_{0}g_{mPass}\left(\frac{1}{g_{dsP}} || (R_{fb1} + R_{fb2})\right)\frac{R_{fb1}}{R_{fb1} + R_{fb2}}$$

(1)

Where  $A_{V_OTA}$  and  $A_{V_P}$  are the voltage gain of the OTA and pass transistor, respectively;  $\beta$  is the feedback factor. The total input transconductance  $G_m = B(g_{mN} + g_{mP})$ , where B is the current gain;  $g_{mN}$  and  $g_{mP}$  are the transconductance of the paralleled complementary input differential pairs.  $g_{mPass}$  is the transconductance of the pass transistor.

The dominant and non-dominant poles of the feedback loop can be given as

$$f_{d} = \frac{1}{2\pi R_{0}C_{0}}$$

(2)

$$f_{nd} = \frac{1}{2\pi \left( \frac{1}{g_{dsP}} \left( R_{fb1} + C_{fb2} \right) \right)_{out}}$$

(3)

The gain bandwidth product (GBW) of the feedback loop can be obtained from equations (1) and (2)

$$GBW = LG \times f_{d} = \frac{G_{m}A_{V_{\perp}P}\beta}{2\pi C_{0}}$$

(4)

Since the operating state of the pass transistor is dramatically changed with the load current, the small signal gain of the pass transistor  $A_{V_{-}P}$  and the capacitor  $C_0$  at the

ISBN: 978-988-19251-7-6 ISSN: 2078-0958 (Print); ISSN: 2078-0966 (Online) OTA output are dramatically affected. Correspondingly, the non-dominant pole  $f_{nd}$  locating at the LDO voltage output will change with load current, degrading the stability of the feedback loop.

To ensure the stability of the feedback loop and improve the transient response, a Miller compensation capacitor  $C_C$  is adopted for the worst case frequency compensation. The non-dominant pole  $f_{nd}$  should be 3 times beyond the GBW, given as bellow,

$$\frac{1}{2\pi \left( \frac{1}{g_{dsP}} \left( R_{fb1} + C_{fb2} \right) \right)_{out}} > 3 \times \frac{G_{B}}{2\pi C_{c}}$$

(5)

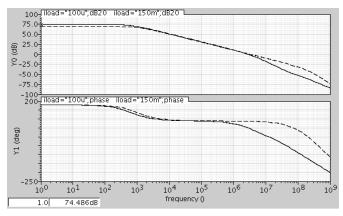

The simulation demonstrates that the capacitor should be 7pF for a minimum load current of  $100\mu$ A. The simulated frequency response of the feedback loop with 7pF Miller compensation capacitor is given in Fig. 4, where the load currents are at the minimum and maximum level respectively.

Fig. 4. Frequency response under different load current

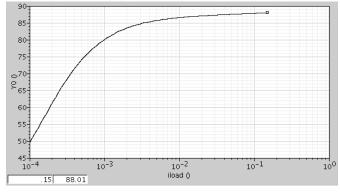

The simulated Phase Margin (PM) under different load current is given in Fig. 5, where the PM is at least 50 degree, ensuring the stability of the feedback loop with load current from  $100\mu$ A to 150mA.

Fig. 5. Phase Margin under different load current

### B. Transient analysis

Comparing with the conventional LDO voltage regulator with off-chip output capacitor of several micro farads, the on-chip LDO uses the power line capacitor of several tens pico farads as the output capacitor. During the load transient between different levels, the feedback loop can't respond Proceedings of the World Congress on Engineering and Computer Science 2011 Vol II WCECS 2011, October 19-21, 2011, San Francisco, USA

immediately; the output voltage is sustained through charging or discharging the output capacitor. Thus, the variation of the output voltage can be given as

$$\Delta V_{out} = \frac{\int_{t_0}^{t_1} i(t)dt}{C_{out}} = \frac{\int_{t_0}^{t_1} [i_{load}(t) - i_{Mp}(t)]dt}{C_{out}}$$

(6)

where  $t_0$  is the moment when the load current changes,  $t_1$  is the moment when the feedback loop settles; the transient current i(t) passing through the output capacitor  $C_{out}$  is the differential current between the load current  $i_{load}(t)$  and the current  $i_{Mp}(t)$  provided by the pass transistor. Even for on-chip output capacitor of 100pF, the variation needs to be controlled within 10% of the output voltage, requiring the feedback loop respond to the load current as fast as possible.

The transient regulation characteristic of the LDO voltage regulator during large current transient depends on the slewing rate (SR) and gain bandwidth product (GBW) of the feedback loop [5]. Large parasitic capacitor at the gate of the pass transistor causes slew effect, degrading load transient response. In the proposed LDO voltage regulator, paralleled input differential pairs and the current amplifiers increase both SR and GBW with a factor of current gain B, thus, the variation of the output voltage is decreased through speeding up transient response during load current transient.

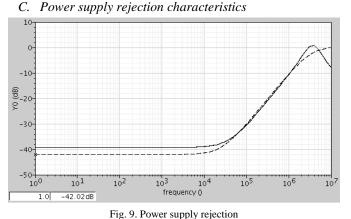

## C. Power supply rejection analysis

For the power supply plagued by noise in the SoC environments, the LDO voltage regulator with a high PSR over a wide frequency range shields noise-sensitive blocks from high frequency ripples in the power supply [6]. However, several paths between the input and output voltage of the LDO voltage regulator cause finite PSR over a limited frequency range [7]. Considering the direct path through the transconductance  $g_{mPass}$  and conductance  $g_{ds}$  of the pass transistor, the PSR of the proposed LDO voltage regulator cause as

$$PSR = \frac{1 + A_{V_{\perp}P}}{1 + \frac{1}{g_{dsP}(R_{fb1} + R_{fb2})} + \frac{1}{sC_{out}} + \frac{LG}{1 + \frac{s}{2\pi f_d}}}$$

(7)

Where  $A_{V_P}$  is the voltage gain of the pass transistor; LG is the loop gain at low frequency;  $f_d$  is the frequency of the dominant pole. Concludingly, the PSR at low frequency is mainly determined by the loop gain. However, the loop gain is reduced at higher frequency due to the dominant pole  $f_d$ , degrading the PSR at higher frequency. To obtain a high PSR over a wide frequency range, both high loop gain and dominant pole of high frequency have to be realized at the same time.

#### **III. SIMULATION RESULTS**

The performance of the proposed LDO voltage regulator is simulated under 0.18µm CMOS technology. The input, output and reference voltage are 3.3V, 1.8V and 1.2V respectively, while the series feedback resistors are  $30k\Omega$  and  $60k\Omega$  with feedback factor of 2/3. The transistor dimensions and bias conditions are summarized in Table I.

| TABLE I.<br>Transistor dimensions and bias condisions |        |       |                           |  |  |  |

|-------------------------------------------------------|--------|-------|---------------------------|--|--|--|

| Transistor                                            | W(µm)  | L(µm) | $I_{D}\left(\mu A\right)$ |  |  |  |

| $M_0$                                                 | 5      | 1     | 20                        |  |  |  |

| M <sub>1</sub> , M <sub>2</sub>                       | 12     | 1     | 10                        |  |  |  |

| M <sub>3</sub> , M <sub>4</sub>                       | 1.5    | 1     | 10                        |  |  |  |

| M <sub>5</sub>                                        | 3×1.5  | 1     | 30                        |  |  |  |

| M <sub>10</sub>                                       | 2      | 1     | 20                        |  |  |  |

| M <sub>11</sub> , M <sub>12</sub>                     | 2      | 1     | 10                        |  |  |  |

| M <sub>13</sub> , M <sub>14</sub>                     | 8      | 1     | 10                        |  |  |  |

| M <sub>15</sub>                                       | 3×8    | 1     | 30                        |  |  |  |

| M <sub>P</sub>                                        | 15×100 | 0.26  | 20                        |  |  |  |

## A. Static-state regulation characteristics

#### Line regulation

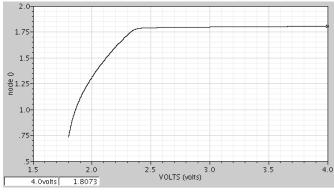

The output voltage of the proposed LDO voltage regulator with the input voltage swept from 1.8V to 4V is given in Fig. 6.

Fig. 6. Line Regulation

The simulation result illustrates that the output voltage variation is 22mV when the input voltage changes from 2.4V to 4V with the drop-out voltage higher than 600mV, resulting in the line regulation of  $13.75\mu$ V/mV.

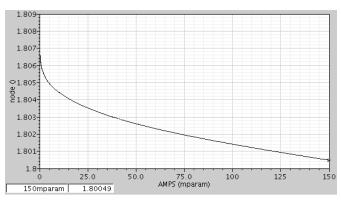

Load regulation

The output voltage of the proposed LDO voltage regulator with the load current swept from 0 to 150mA is given in Fig. 7.

Fig. 7. Load Regulation

Proceedings of the World Congress on Engineering and Computer Science 2011 Vol II WCECS 2011, October 19-21, 2011, San Francisco, USA

The simulation result illustrates that the output voltage variation is 7.6mV with the load current changing from 0 to 150mA, resulting in the load regulation of  $51\mu$ V/mA.

Both line regulation and load regulation specify the static-state regulation characteristics of the output voltage for a given range of input voltage and load current, which can be improved through increasing the feedback loop gain.

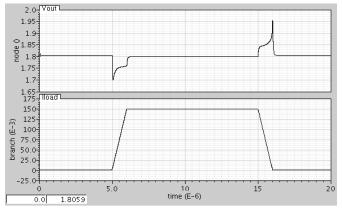

## B. Dynamic-state regulation characteristics

The load transient response of the proposed LDO voltage regulator with 100pF on-chip output capacitor is given by Fig. 8. The load current varies between 1mA and 150mA with rising and falling time of  $1\mu$ s.

Fig. 8. Load transient response

The simulation results illustrate that the output voltage variation is 108 mV, 153 mV respectively; with settling time of  $1.2\mu$ s,  $1.4\mu$ s.

——solid for  $I_{load}=100\mu$ A; -----dashed for  $I_{load}=150$ mA)

The power supply rejection under minimum and maximum load currents is given in Fig. 9. The simulated result illustrates that the PSR is around -40dB at low frequency and -30dB at frequency of 100 kHz.

## D. Summarized characteristics and comparisons

The characteristics of the proposed on-chip LDO voltage regulator with 100pF on-chip output capacitor are summarized in Table II, and compared with references [2], [3] and [4] implemented in  $0.35\mu m$  CMOS technology.

| SUMMARY AND COMPARISON    |              |        |               |                    |  |

|---------------------------|--------------|--------|---------------|--------------------|--|

| Paper                     | [2]          | [3]    | [4]           | This work          |  |

| C <sub>com</sub> (pF)     | 6            | 21     | 7             | 7                  |  |

| Ι <sub>Q</sub> (μΑ)       | 100          | 65     | 20            | 90                 |  |

| I <sub>load</sub> (mA)    | 100          | 50     | 100           | 150                |  |

| Line<br>regulation        | 344<br>μV/V  | 1%     | 57.4<br>μV/mV | 13.75<br>μV/mV     |  |

| Load<br>regulation        | 388<br>μV/mA | 2%     | 109<br>μV/mA  | 51<br>μV/mA        |  |

| ΔV <sub>out</sub><br>(mV) | <50          | <90    | <100          | <155               |  |

| Δt(μs)                    | 30           | 15     | 9             | <1.4               |  |

| PSR(dB)                   | NA           | -55@DC | -40@10k       | -40@DC<br>-30@100k |  |

TABLE II.

## IV. CONCLUSION

The proposed on-chip LDO voltage regulator implemented in 0.18 $\mu$ m CMOS technology realizes DC voltage conversion between 3.3V and 1.8V with 150mA driving capability while consuming only 90 $\mu$ A quiescent current. The load transient can be recovered within 1.4 $\mu$ s with variation within 10% of the output voltage.

### ACKNOWLEDGMENT

The author would like to thank Guo Wei for his discussions and technical supports on the LDO voltage regulator design.

#### REFERENCES

- [1] Dennis D. Buss, "Technology in the Internet Age," ISSCC 2002

- [2] S. K. Lau, P. K. T. Mok, and K. N. Leung, "A low-dropout regulator for SoC with Q-reduction," *IEEE J. Solid-State Circuits*, vol. 42, no. 3,pp. 658–664, Mar. 2007.

- [3] R. J. Milliken, J. Silva-Martínez, and E. Sánchez-Sinencio, "Full on-chip CMOS low-dropout voltage regulator," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 9, pp. 1879–1890, Sep. 2007.

- [4] Edward N. Y. Ho and Philip K. T. Mok, "A Capacitor-Less CMOS Active Feedback Low-Dropout Regulator With Slew-Rate Enhancement for Portable On-Chip Application," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 57, no. 2, pp. 80–84, Feb. 2010.

- [5] C. T. Chuang, "Analysis of the settling behavior of an operational amplifier," *IEEE J. Solid-State Circuits*, vol. SC-17, NO.1, pp. 74–80, Feb. 1982.

- [6] V. Gupta and G. A. Rincon-Mora, "A Low Dropout, CMOS regulator with High PSR over Wideband Frequencies," *ISCAS*, vol. 5, pp. 4245-4248, 2005.

- [7] Mohamed El-Nozahi, Ahmed Amer, Joselyn Torres, Kamran Entesari, and E. Sánchez-Sinencio, "High PSR Low Drop-Out Regulator With Feed-Forward Ripple Cancellation Technique," *IEEE J. Solid-State Circuits*, vol. 45, NO.3, pp. 565–577, Mar. 2010